Failure Analysis of EDN337N FET

Gideon Analytical labs received one FDN337N-channel FET for failure analysis. The Drain-Source was reported shorted. Super SOTTM-3 N-Channel logic level enhancement mode power field effect transistors are produced using Fairchild’s high cell density DMOS technology. This very high-density process is specially tailored to minimize on-state resistance.

These devices are particularly suited for low voltage applications in notebook computers, portable phones, PCMCIA cards, and other battery powered circuits where fast switching and low in-line power loss are needed in a very small outline surface mount package.

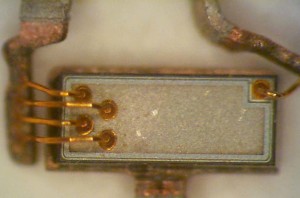

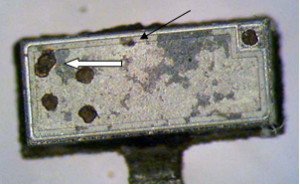

The plastic was removed to reveal the following:

- One of the source wires to the left was fused with the silicon (excessive inrush current)

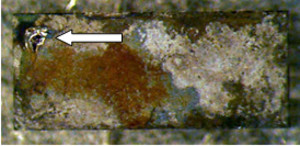

- Near the top edge of the step oxide coverage, there is a catastrophic electrical overstress (EOS) which shorted the terminals

- Considerable heat damage was evident on oxide layer die melting the aluminum source metal. The current was too high in this application for the FET rating.

Gideon Analytical labs can save valuable time when debugging a new design and determining the failure mode. If you need failure analysis on FETs or other components call Gideon.

Field Effect Transistor

Decapsulated die

New FET

Melted metal and EOS site

Excessive heat caused cracking